Quick Facts

- Category: Science & Space

- Published: 2026-05-03 18:26:31

- Mastering SAP-Related npm Packages Compromised in Credential-Stealing Supply ...

- Mastering the Model Context Protocol: From Basics to Full-Stack Applications

- Warp Terminal Opens Up: AI-Powered Contributions and Community Engagement

- Cybercrime Group TeamPCP Launches CanisterWorm Wiper Attack Against Iranian Systems

- Your Complete Guide to Buying the Motorola Razr Fold: Price, Availability, and Pre-Order Steps

The Miniaturization Paradox: Smaller Usually Means Hotter

For decades, the electronics industry has pursued smaller components to pack more power into devices. But as transistors and memory cells shrink, they face a fundamental problem: increased energy loss and heat generation. This paradox has limited how small we can make high-performance chips without sacrificing battery life or risking overheating.

Traditional memory technologies like DRAM and NAND flash suffer from leakage currents and higher resistance at nanoscale dimensions. The smaller the cell, the more energy escapes as heat—a major hurdle for smartphones, wearables, and AI accelerators that demand both compact size and long battery life. Engineers have wrestled with this trade-off for years, often accepting that miniaturization comes with a thermal penalty.

A New Memory Chip That Flips the Script

Now, researchers have unveiled a memory device that breaks this rule entirely. Instead of increasing energy loss when shrunk, this chip becomes more efficient. The team achieved this by redesigning the fundamental structure of the memory cell and scaling components to an extreme level—something once considered impossible.

The result is a tiny memory unit that not only retains data reliably but also reduces power consumption as its dimensions decrease. This counterintuitive behavior opens the door to ultra-efficient electronics that run cooler and longer than ever before.

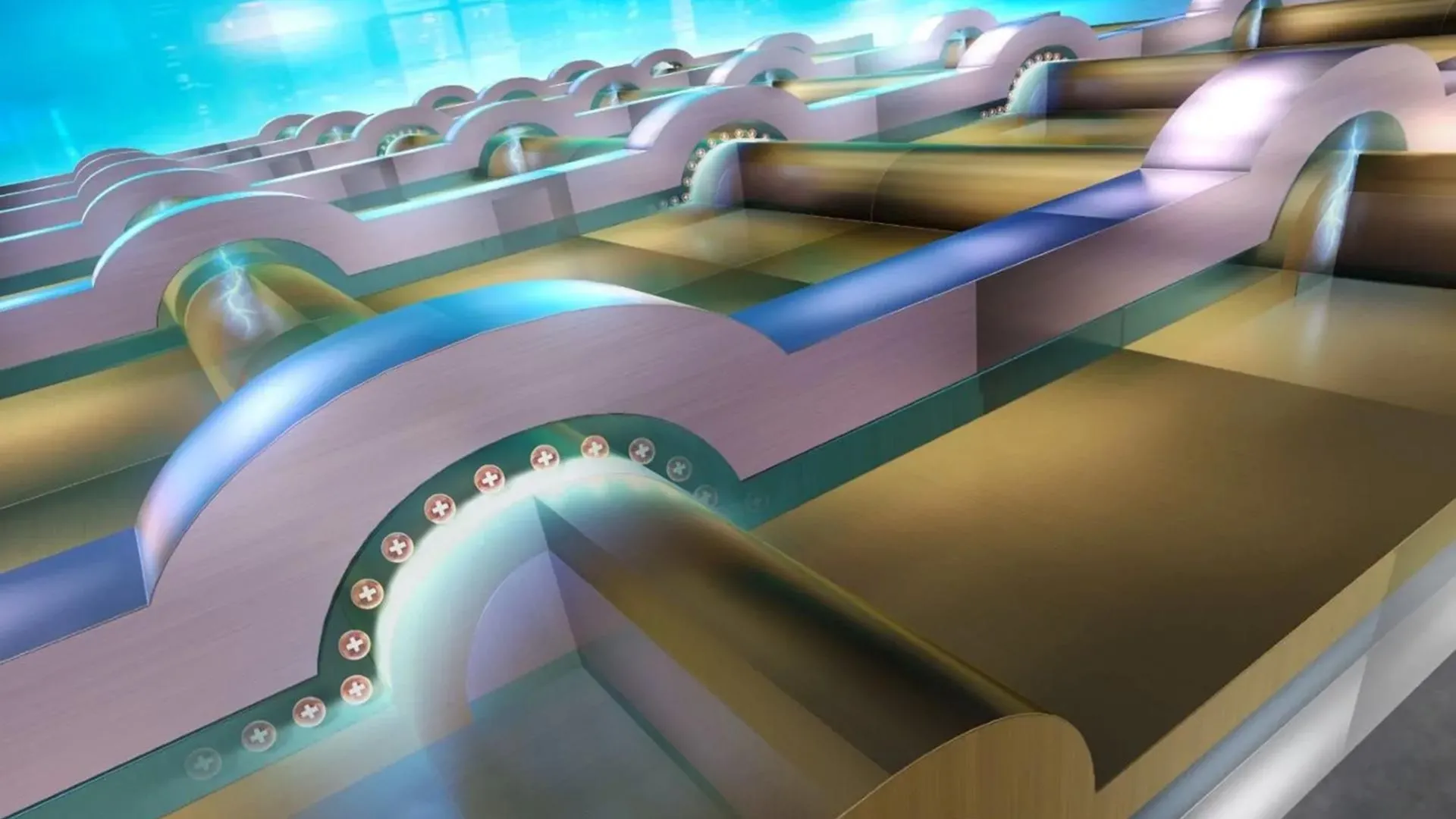

How It Works: Rethinking Memory Cell Architecture

The breakthrough hinges on a novel approach to memory cell design. Traditional cells rely on a transistor-capacitor or floating-gate structure, where shrinking the physical size increases parasitic capacitance and leakage. The new chip uses a resistive switching mechanism combined with atomically thin materials that behave differently at the nanoscale.

Specifically, the researchers engineered a vertical, 3D-like architecture that confines electrons more tightly, preventing energy from escaping. As the cell shrinks, the surface-to-volume ratio changes in a way that actually improves charge retention and reduces switching energy. This is the opposite of what happens in conventional memory.

Key technical details include:

- Use of layered transition metal dichalcogenides (like MoS₂) as the switching medium.

- An ultra-thin insulator less than 1 nm thick, enabling low-voltage operation.

- A self-aligned fabrication process that minimizes defects at the edges.

These innovations allow the memory cell to maintain stable performance down to just a few atoms wide—a scale where conventional cells would fail.

What This Means for Future Devices

This technology could transform how we design electronics. Smartphones might run for days on a single charge instead of hours. Wearables like smartwatches and medical patches could become thinner and more powerful without overheating. AI systems, which rely on vast memory arrays, could operate more efficiently in data centers and edge devices alike.

Beyond consumer gadgets, the chip holds promise for Internet of Things (IoT) sensors that need to run for years on tiny batteries, and for spacecraft where every milliwatt counts. The ability to shrink memory without energy penalties also means higher density storage—potentially terabytes of memory in a chip smaller than a fingernail.

Remaining Challenges

While the lab results are promising, scaling this technology to mass production is not trivial. The researchers need to prove that the chips can be manufactured with consistent quality across billions of cells. They also must ensure endurance—how many write cycles the memory can withstand—and data retention over years without power. Early tests show excellent durability, but more work is needed.

Paving the Way for a New Era of Electronics

This memory chip represents a fundamental shift in our understanding of miniaturization. By proving that components can become more efficient as they shrink, it challenges decades of engineering assumptions. If commercialized, it could unlock a new generation of ultra-efficient devices that are smaller, faster, and cooler than anything available today. The researchers plan to continue refining the design and exploring partnerships with chip manufacturers to bring this technology to market within the next few years.

For more insight into how this compares with other emerging memory technologies, see our article on the miniaturization paradox and future device implications.